Designprocessen för digital hårdvara har förändrats intensivt under de senaste åren. Så små digitala kretsar kan implementeras med PAL och PLA. Varje enhet används för att implementera olika kretsar som inte behöver mer än antalet i / ps, o / ps och produktvillkor som erbjuds i det specifika chipet. Dessa marker är otillräckliga till ganska blygsamma storlekar, som normalt stöder ett ömsesidigt antal in- och utgångar på högst 32. För utformning av dessa kretsar som behöver mer in- och utgångar kan antingen många PLA / PAL användas eller annars en mer stilig typ av chip kan användas som kallas CPLD (komplex programmerbar logisk enhet). Ett CPLD-chip innehåller flera kretsblock på ett chip med inre ledningsresurser för att fästa kretsblocken. Varje kretsblock kan jämföras med en PLA eller en PAL.

Vad är en komplex programmerbar logisk enhet?

Förkortningen för CPLD är 'Komplexa programmerbara logiska enheter', det är en typ av integrerad krets som applikationsdesigners designar för att implementera digital hårdvara som mobiltelefoner. Dessa kan hantera medvetet högre mönster än SPLD (enkla programmerbara logiska enheter), men erbjuder mindre logik än FPGA ( fältprogrammerbara grindmatriser CPLD inkluderar flera logiska block var och en av blocken innehåller 8-16 makroceller. Eftersom varje logikblock utför en specifik funktion är alla makroceller i ett logikblock helt anslutna. Beroende på användning kan dessa block vara anslutna till varandra eller inte.

Komplex programmerbar logisk enhet

De flesta CPLD: er (komplexa programmerbara logiska enheter) har makroceller med en summa av logisk funktion och ett val FF (flip-flop) . Beroende på chip stöder den kombinatoriska logikfunktionen från 4 till 16 produkttermer med inkluderande fan-in. CPLD skiljer sig också åt när det gäller skiftregister och logiska grindar. Av denna anledning kan CPLD med ett stort antal logiska grindar användas istället för FPGA. En annan CPLD-specifikation anger antalet produkttermer som en makrocell kan åstadkomma. Produkttermer är produkten av digitala signaler som utför en specifik logisk funktion.

CPLDs finns i flera IC-paketformulär och logiska familjer. CPLD skiljer sig också åt när det gäller matningsspänning, driftsström, standbyström och strömavledning. Dessutom kan dessa erhållas med olika mängder minne och olika typer av minnesstöd. Vanligtvis uttrycks minnet i bitar / megabit. Minnesstöd består av ROM, RAM och dual-port RAM. Den består också av CAM (innehållsadresserbart minne) samt FIFO (först in, först ut) minne och LIFO (sista in, sista ut) minne.

Arkitektur för komplexa programmerbara logiska enheter

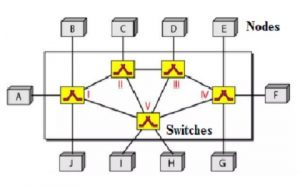

En komplex programmerbar logisk anordning består av en grupp av programmerbara FB: er (funktionella block). In- och utgångarna från dessa funktionella block är sammankopplade med en GIM (global samtrafikmatris). Denna sammankopplingsmatris kan omkonfigureras så att vi kan modifiera kontakterna mellan funktionsblocken. Det kommer att finnas några in- och utgångsblock som låter oss förena CPLD till den externa världen. Arkitekturen för CPLD visas nedan.

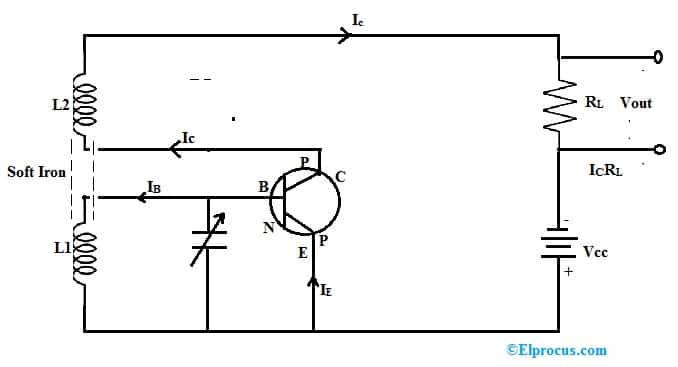

Generellt ser den programmerbara FB ut som matris med logiska grindar där en uppsättning OCH-grindar kan programmeras och ELLER grindar är stabila. Men varje tillverkare har sitt sätt att tänka för att utforma det funktionella blocket. En listad o / p kan hittas genom att man använder de återkopplingssignaler som uppnås från ELLER grindutgångarna.

CPLD-arkitektur

Vid CPLD-programmering kodas designen först på Verilog- eller VHDL-språket när koden är (simulerad och syntetiserad. Under syntes handplockas CPLD-modellen (målenheten) och en teknikbaserad mappningslista produceras. Denna lista kan vara nära -anpassning till den äkta CPLD-arkitekturen med en plats- och ruttprocess, vanligtvis uppnådd med plats-och-ruttprogramvaran för CPLD Company: s egenutvecklade. Då gör operatören några bekräftelseprocesser. Om allt är bra kommer han att använda CPLD, annars han kommer att ordna om det.

Arkitekturfrågor av CPLD

När man överväger en komplex programmerbar logisk enhet för användning i design finns det några följande arkitekturproblem kan tas med i beräkningen

- Programmeringstekniken

- Funktionsblocksförmågan

- I / O-förmågan

Några av familjerna i CPLD från olika återförsäljare inkluderar

- Altera MAX 7000 och MAX 9000 familjer

- Atmel ATF- och ATV-familjer

- Gitter isp LSI familj

- Gitter (Vantis) MACH-familjen

- Xilinx XC9500-familjen

Familjer till CPLD

Tillämpningar av CPLD

Tillämpningarna av CPLD inkluderar följande

- Komplexa programmerbara logiska enheter är idealiska för kritiska styrapplikationer med hög prestanda.

- CPLD kan användas i digital design för att utföra funktioner som startladdare

- CPLD används för att ladda konfigurationsdata för en fältprogrammerbar grindmatris från icke-flyktigt minne.

- I allmänhet används dessa i små designapplikationer som adressavkodning

- CPLD används ofta många applikationer som i kostnadskänsliga, batteridrivna bärbara enheter på grund av dess låga storlek och användning av låg effekt.

Detta handlar alltså om komplex programmerbar logisk enhetsarkitektur och dess applikationer. Vi hoppas att du har fått en bättre förståelse för detta koncept. Dessutom är alla frågor angående detta koncept eller för att genomföra elektriska och elektroniska projekt , ge dina värdefulla förslag genom att kommentera i kommentarsektionen nedan. Här är en fråga till dig, vad är skillnaden mellan CPLD och FPGA?

Fotokrediter:

- CPLD wikimedia

- Arkitektur av CPLD slidesharecdn

![Icke-kontakt AC-fasdetektorkrets [testad]](https://electronics.jf-parede.pt/img/sensors-detectors/38/non-contact-ac-phase-detector-circuit.png)