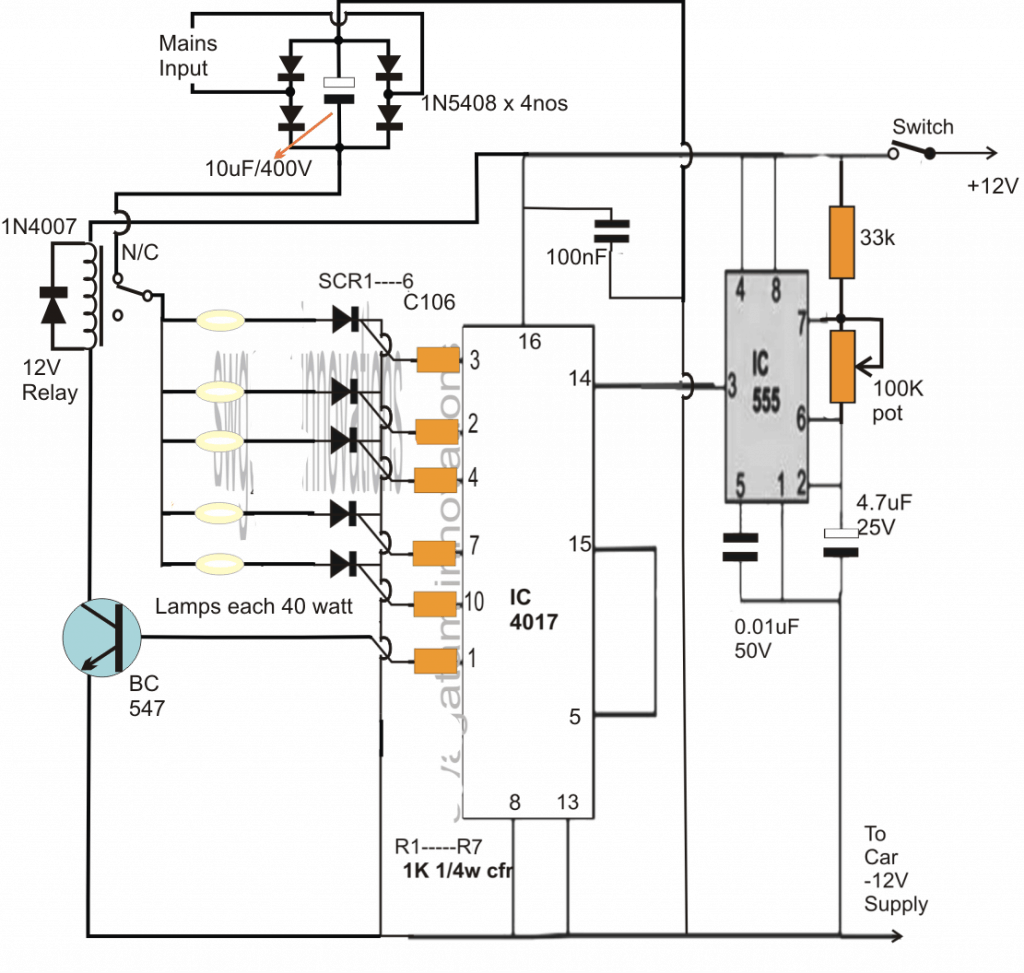

De kombinationskretsar inte använda någon form av minne. Därför inkluderar det tidigare ingångsläget inget resultat över kretsens nuvarande situation. Även om den sekventiella kretsen inkluderar minne beror följaktligen utgången på ingång vilket betyder att utgången kan förändras baserat på ingången. Arbetet med dessa kretsar kan göras genom att använda tidigare kretsingång, CLK, minne och utgång. Den här artikeln diskuterar en översikt av master-slave-flip-flop. Men innan du lär känna till denna flip-flop, måste man veta om grunderna i Flip flops som SR flip flop och JK flip flop.

Vad är en Master-Slave Flip Flop?

I grund och botten kan denna typ av flip flop utformas med två JK FF genom att ansluta i serie. En av dessa FF: er, en FF fungerar som befälhavare och andra FF fungerar som slav. Anslutningen av dessa FF kan göras så här, master FF-utgången kan anslutas till ingångarna till slaven FF. Här kan slav FF: s utgångar anslutas till ingångarna till master FF.

I denna typ av FF, en växelriktare används också förutom två FF: er. Inverteranslutningen kan göras på ett sådant sätt att där den inverterade CLK-pulsen kan anslutas till slaven FF. Med andra ord, om CLK-pulsen är 0 för en master-FF, kommer CLK-pulsen att vara 1 för en slav-FF. På liknande sätt, när CLK-pulsen är 1 för master FF, kommer CLK-pulsen att vara 0 för slav FF.

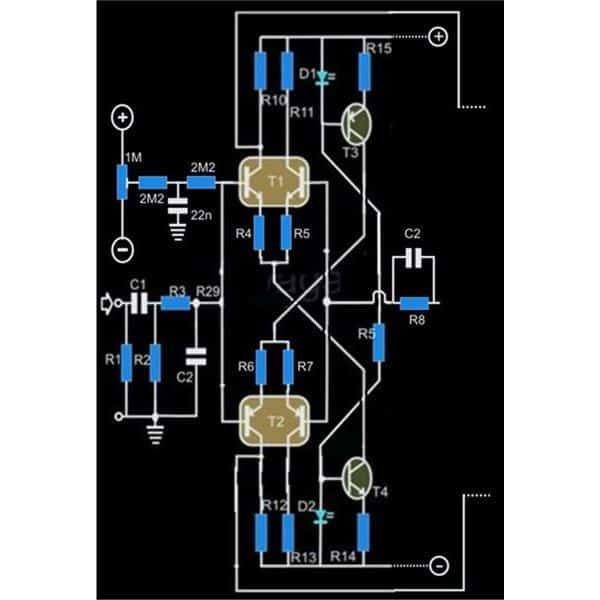

master-slave-flip-flop-circuit

Master-Slave FF arbetar

När CLK-pulsen går till hög vilket betyder 1, kan slaven separeras. Ingångarna som J & K kan ändra systemets tillstånd.

Slaven FF kan lossas tills CLK-pulsen går till låg vilket betyder 0. Närhelst CLK-pulsen går tillbaka till lågt tillstånd kan data överföras från master FF till slaven FF och slutligen o / p kan erhållas.

Först utlöses master FF på en positiv nivå medan slaven FF utlöses på en negativ nivå. Av denna anledning svarar master FF först.

Om J = 0 & K = 1, så går utgången från master FF 'Q' till ingången K för slaven FF & CLK tvingar slaven FF till RST (återställning), därför slav FF kopierar master FF.

Om J = 1 & K = 0, går master FF 'Q' till ingången J på slaven FF & CLK: s negativa övergång ställer in slaven FF och kopierar mastern.

Om J = 1 & K = 1, växlar den över CLK: s positiva övergång och därför slår slaven över CLK: s negativa övergång.

Om båda J & K är 0, kan FF immobiliseras och Q förblir omöjlig.

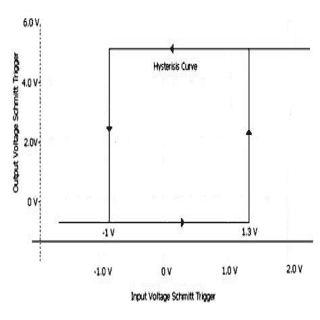

Timing Diagram

- När både CLK-puls & o / p för mastern är hög, förblir den hög tills CLK är låg på grund av att tillståndet är lagrat.

- För närvarande blir masterns o / p låg då CLK-pulsen blir hög igen och förblir låg tills CLK blir hög igen.

- Växling sker därför för en CLK-cykel.

timing-diagram-av-en-master-slav-FF

- När CLK-pulsen är 1, ställs master in men inte slaven, därför förblir slaven o / p '0' tills CLK förblir 1.

- När CLK är låg, blir slaven till operationell och förblir '1' tills CLK återigen blir till '0'.

- Växling sker under hela proceduren medan o / p ändras en gång inom en cykel.

- Detta gör denna vippa som en synkron apparat eftersom den endast skickar data med CLK-signaltimingen.

Således handlar det här om Master-Slave Flip Flop . Från ovanstående information kan vi slutligen dra slutsatsen att denna FF kan byggas med två FF: er, nämligen master och slave. När en FF fungerar som huvudkretsen aktiveras den över framkanten av CLK-pulsen. På liknande sätt, när en annan FF fungerar som slavkretsen, aktiveras den över CLK-pulsens fallande kant.