Den största nackdelen med kombinationskrets är, det använder inget minne för att spara nuvarande och tidigare tillstånd. Följaktligen har det tidigare ingångstillståndet ingen effekt på kretsens nuvarande tillstånd. Den sekventiella kretsen har minne så att utdata kan variera beroende på ingång. Denna typ av kretsar använder tidigare ingång, utgång, klocka och ett minneselement. Här kan minneselementen vara spärr eller flip-flops. Sekventiella kretsar är designade med olika metoder som genom att använda ROM och flip, PLA, CPLDs (Complex Programmable Logic Device) , FPGA: er (fältprogrammerbar grindmatris) . I den här artikeln ska vi bara diskutera hur man utformar en sekventiell krets med hjälp av PLA.

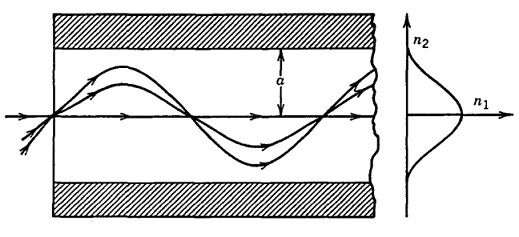

Blockdiagrammet för den sekventiella kretsen som visas nedan:

Blockdiagram över sekventiell krets

Utformning av sekventiell krets med hjälp av PLA

Sekventiella kretsar kan realiseras med hjälp av PLAs (Programmable Logic Arrays) och flip-flops. I denna design kan tillståndstilldelningen vara viktig eftersom användningen av en god tillståndstilldelning kan minska det erforderliga antalet produkttermer och därmed minska den nödvändiga storleken på PLA. En produktterm definierad som sammankopplingen av bokstäver, där varje bokstav antingen är en variabel eller dess negation.

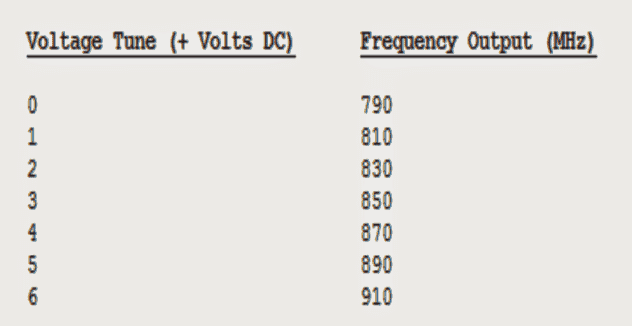

För låt oss betrakta designen som en kodomvandlare. Tillståndstabellen som visas nedan i tabellen kan realiseras med en PLA och tre Flip flops som visas nedan. Denna kretskonfiguration liknar mycket ROM-flip-flop-baserad design, förutom att ROM ersätts av PLA av lämplig storlek. Statstilldelningen leder till sanningstabellen nedan. Denna tabell kan lagras i en PLA med fyra ingångar, 13 produkttermer och fyra utgångar, men detta skulle ge lite mindre storlek jämfört med 16-ords-ROM.

| X Q1 Q2 Q3 | Med D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabell: Sanningstabell

NÄRVARANDE STAT

| NÄSTA STAT X = 0 1 | NÄRVARANDE UTGÅNG (Z) |

| TILL | FÖRE KRISTUS | 1 0 |

B C | D E Och E | 1 0 0 1 |

D ÄR | H H H M | 0 1 1 0 |

H M | A A TILL - | 0 1 1 - |

Tabell: State Table

Utformning av sekventiella kretsar med PLA

Ingångsutgångsekvationer härledda av Karnaugh Map

Här, eftersom det finns sju stater, krävs tre D-flip-flops. Således krävs en PLA-krets med 4 ingångar och 4 utgångar. Om kodomvandlarens tillståndstilldelning beaktas, kan den resulterande utgångsekvationen och D-flip-flop-ingångsekvationer härledda från Karnaugh skrivas följande ekvationer

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | Med D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 elva

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

PLA-tabellen som motsvarar dessa ekvationer ges i tabellen ovan. Denna tabell kan realiseras genom att använda PLA med fyra ingångar, sju produkttermer och fyra utgångar. För att verifiera funktionen hos ovanstående design antar du att X = 0 och Q1Q2Q3 = 000. Detta markerar rader - - 0- och 0 - - -0 i tabellen, så Z = 0 och D1D2D3 = 100. Efter den aktiva klockkanten är Q1Q2Q3 = 100. Om nästa ingång är X = 1 väljs rader - - 0 - och - 1- - så Z = 0 och D1D2D3 = 110. Efter den aktiva klockkanten är Q1Q2Q3 = 110.

Programmerbar logisk matris (PLA)

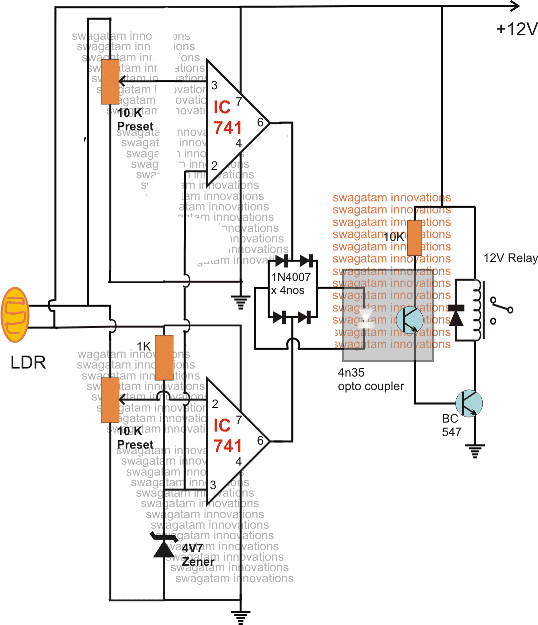

Programmable Logic Array är en programmerbar logisk enhet. Det används vanligtvis för att implementera kombinationslogiska kretsar. PLA har en uppsättning programmerbara AND-plan (AND-array), som länkar till en uppsättning programmerbara OR-plan (OR-array), som sedan kan kompletteras provisoriskt för att producera en utgång. Denna layout gör det möjligt att syntetisera ett stort antal logiska funktioner i summan av produkter (SOP) kanoniska former. Ett enkelt blockschema över en PLA ges nedan.

Blockdiagram över en PLA

Huvudskillnaden mellan PLA och PAL (programmerbar arraylogik) är,

PLA: Båda OCH plan och ELLER plan är programmerbara.

PAL: Endast AND-planet är programmerbart, medan OR-planet är fixerat.

För bättre förståelse av PLA, här överväger vi nedanstående exempel.

Låt oss försöka implementera dessa funktioner f1 och f2 ges som

Ingångarna x1, x2, x3 och deras respektive kompletterade signaler ges till programmerbara OCH-plan, där får vi OCH-planutgångar som P1, P2, P3-kallade mintermer. Därefter ges dessa signaler till programmerbart ELLER-plan för att producera erforderlig utgångsfunktion fl och f2 (summan av produkter). Figuren nedan beskriver grindenivåimplementeringen av PLA för given funktionalitet.

Implementering av PLA

Det här handlar om att designa sekventiella kretsar med PLA. Vi anser att informationen i den här artikeln är till hjälp för en bättre förståelse av detta koncept. Dessutom har alla frågor angående denna artikel eller någon hjälp med genomförande av el- och elektronikprojekt kan du kontakta oss genom att kommentera i kommentarsektionen nedan. Här är en fråga till dig, Vad menas med en sekventiell krets?