Termen VLSI står för ”Very Large Scale Integration Technology” som innebär att man utformar integrerade kretsar (ICs) genom att kombinera tusentals transistorer logiskt in i ett enda chip av olika logiska kretsar . Dessa IC minskar så småningom det upptagna kretsutrymmet jämfört med kretsarna med konventionella IC. Beräkningskraft och rymdutnyttjande är de viktigaste utmaningarna i VLSI-designen. Genomförandet av VLSI-projekt öppnar en utmanande och ljus karriär för studenter såväl som forskare. Några av de nya trendområdena för VLSI är på-plats-programmerbar grindmatris applikationer (FPGA), ASIC-design och SOC. En lista över några av VLSI-projekten ges nedan för de studenter som uppriktigt söker projekt inom detta område. Den här artikeln diskuterar en översikt över VLSI-projekt baserade på FPGA, Xilinx, IEEE, Mini, Matlab, etc. listas nedan. Dessa projekt är till stor hjälp för ingenjörsstudenter, M.tech-studenter.

VLSI-projekt för ingenjörsstudenter

VLSI-projekt med abstrakt för studenter inom elektronikteknik diskuteras nedan.

VLSI-projekt

1). Transformation of Discrete Wavelet-baserad på 3D-lyft

Detta projekt hjälper till att tillhandahålla mycket exakta bilder genom att använda kodningen av en bild utan att förlora dess data. För att uppnå detta implementerar denna process ett lyftfilter beroende på omvandlingen av 3D-diskret wavelets VLSI-arkitektur.

2). Utformning av SFQ-multiplikator med 4-bitars med effektivt genom höghastighetshårdvara

Detta projekt används huvudsakligen för att implementera en modifierad monterkodare (MBE) med 4-bitars SFQ-baserad multiplikator . Denna multiplikator ger bra prestanda jämfört med den konventionella monterkodaren. Detta projekt används huvudsakligen i applikationer med kritisk fördröjning.

3). Kryptografiprocessor som används i smartkort med ett effektivt område

Detta projekt används för att implementera tre kryptografialgoritmer som stöds av både privata och offentliga nycklar som används i smart kort applikationer för att tillhandahålla extremt säker användarverifiering och data kommunikation .

4). En höghastighets- eller lågeffektsmultiplikator med Spurious Power Suppression Method

Detta föreslagna systemet filtrerar bort de värdelösa falska signalerna från aritmetiska enheter för att undvika onödig dataöverföring som inte påverkar de senaste beräkningsresultaten. Detta system använder en SPST-metod för multiplikatorer för att uppnå dataöverföring med låg effekt och höghastighet.

5). Komprimering och dekompression av en förlustfri algoritm

Detta projekt implementeras huvudsakligen för 2-stegs hårdvaruarkitektur beroende på PDLZW (Parallel Dictionary LZW) algoritmfunktion samt Adaptive Huffman-typalgoritmen som används för både applikationer av förlustfri datakomprimering och förlustfri dekompression.

6). Arkitekturen för Turbo-avkodare med låg komplexitet för energieffektiva WSN

Det föreslagna systemet används för att minska den totala energiförbrukningen genom dataöverföring av WSN genom den sönderfallande algoritmen för LUT-Log-BCJR till grundläggande ACS-operationer (Add Compare Select).

7). VLSI-arkitektur för att effektivt ta bort impulsljud från en bild

Detta föreslagna systemet används främst för att förbättra bildkvaliteten visuellt för att undvika risken för att bli skadad med impulsbrus för att implementera en effektiv VLSI-arkitektur med hjälp av ett kantbevarande filter.

8). Arkitekturen för en minnesprocessor som används för komprimering av multimedia

Detta föreslagna systemet ger en låg komplexitet för en processor i minnet för att stödja multimediaapplikationer, nämligen bildkomprimering, video genom att tillämpa enorma enkelinstruktioner, flera datakoncept och instruktionsord.

9). Tidssynkroniseringsteknik med en symbolhastighet för trådlösa OFDM-system med låg effekt

Detta föreslagna systemet används främst för att förbättra funktionen av trådlös OFDM (Orthogonal Frequency Division Multiplexering ) systemet genom att minska basbandseffekten med hjälp av en klocka generator med fasavstämbar och dynamisk samplingsstyrning.

10). Ackumulatorbaserad implementering med låg effekt och höghastighetsmultiplikator med SPST Adder & Verilog

Detta projekt används för att utforma en lågeffekts- och höghastighets-MAC (multiplikator och ackumulator) genom att acceptera den falska dämpningsmetoden för ström på en MBE (modifierad monterkodare). Genom att använda denna design kan strömförlusten för hela omkopplingen undvikas.

11). Robotprocessordesign och implementering genom att möjliggöra antikollision med RFID-teknik

Det föreslagna systemet används främst för att implementera en robotprocessor med antikollision för att undvika den fysiska kollisionen mellan robotar i multirobotmiljön. Denna algoritm implementeras huvudsakligen med VHDL & RFID-teknik.

12). Utformning av logisk krets med krafteffektiv med Adiabatic Method

Detta system demonstrerar logikkretsdesignen effektivt med adiabatisk metod jämfört med konventionell CMOS-design med hjälp av kretsar som använder NAND & NOR grindar . Genom att använda den adiabatiska metoden kan strömförbrukningen i nätverket reduceras såväl som att den återvinner den lagrade energin i lastkondensatorn.

3). Krypteringssystem för att förbättra systemets beräkningshastighet

Huvudintentionen med detta projekt är att förbättra säkerheten för dataöverföring för att förbättra datorhastigheten genom att implementera AES-algoritmen med hjälp av FPGA. Så denna simulering, såväl som matematisk design, kan utföras med hjälp av VHDL-koden.

14). IP-block för AHM eller Advanced High-Performance Bus

Detta projekt används främst för att utforma en arkitektur för Advanced Microcontroller Buss (AMB) med AHBN (Advanced High-Performance Bus). Detta projekt kan utformas med VHDL-kod genom att implementera blocken som master & save.

15). DSM-baserad Multimode RF-sändtagare med en flerkanalig

Detta system används främst för att designa en multimode-sändar- och mottagararkitektur och RF-flerkanal med Delta-Sigma-modulator. Detta föreslagna systemet använder ett VHDL-språk för att implementera två arkitekturer.

16). Koncentratorn för knockout-switch med ett asynkron överföringsläge

Genom att använda detta projekt kan en knockout-switch baserad på asynkron överföring designas med hjälp av verktyg som VHS & VHDL. Denna knock-out-omkopplare kan användas i nätverk för virtuella kretspaket såväl som applikationer för datagram.

17). Asynkrona kretsar Beteendesyntes

Detta projekt används huvudsakligen för att tillhandahålla den beteende-syntesteknik som används för asynkrona kretsar. Båda mallarna som balsa och asynkrona implementeringar är huvudelementen i designen.

18). AMBA Design med AHB-kompatibla minneskontroller

Detta projekt används för att utforma en MC (minneskontroll) beroende på AMBA (Advanced Microcontroller Bus Architecture) för systemminneskontroll med huvudminne som SRAM & ROM.

19). Carry Tree Adder Implementation

Carry tree adder baserad på VLSI-design kallas som de bästa prestandatillsatsarna kontrasterade med vanliga binära adders. De tillägg som implementeras av detta projekt spänner över träd, kogge-sten och gles kogge-sten.

20). CORDIC designbaserad rotation av fast vinkel

Huvudkonceptet för detta föreslagna system är att vrida vektorer med fasta vinklar. Dessa vinklar är nödvändiga för spel, robotik, bildbehandling , etc. Genom att använda detta projekt kan vektorrotation uppnås genom att använda specifika vinklar genom utformningen av CORDIC (koordinatrotations digital dator).

21). FIR-filterdesign med distribuerad aritmetik av uppslagstabellen

Detta föreslagna systemet förbättras främst FIR-filter prestanda genom att designa den med distribuerad aritmetik av en tredimensionell uppslagstabell istället för multiplikatorn. Så den här designen kan implementeras med programvaror som FPGA & Xilinx.

22). Push-Pull-pulsade spärrar med hög hastighet och låg effekt

Detta projekt används för att utföra energieffektiva och högpresterande pulsade spärrar som huvudsakligen används för VLSI-system med hjälp av ny topologi. Eftersom denna topologi huvudsakligen beror på ett sista steg push-pull-driven med två delningsfält genom en villkorlig pulsgenerator.

23). Aritmetic Coder VLSI Architecture in SPIHT

Detta föreslagna systemet förbättrar genomströmningen av metoden för aritmetisk kodning vid uppsättning av partitionering i hierarkiska träd (SPIHT) bildkomprimering med höghastighetsarkitekturen beroende på FPGA.

24). Bullerdämpning av EKG-signal baserat på FPGA

Detta projekt används för att innehålla bruset i EKG-signaler genom två medianfilter med 91 respektive 7 samplingsstorlekar. Så denna process kan uppnås genom att implementera FPGA-design baserat på VHDL-kod.

25). VLSI-baserad högpresterande bildskalningsprocessor med låg kostnad

Detta projekt används för att implementera en algoritm för bildskalningsprocessor baserad på VLSI med mindre minne och hög prestanda. Den föreslagna systemdesignen innehåller huvudsakligen en kombination av filter, omkonfigurerbara dynamiska metoder och hårdvarudelning för att minska kostnaden.

26). Systolisk matrisarkitektur Design och implementering effektivt

Huvudkonceptet för detta projekt är att designa en hårdvarumodell som används för systolisk arraymultiplikator. Denna array kan huvudsakligen användas för att utföra binär multiplikation med hjälp av VHDL-plattformen. Den föreslagna systemdesignen kan implementeras med FPGA & Isim-programvaran.

27). QPSK Design & Synthesis med VHDL-kod

QPSK är en av de viktigaste moduleringsmetoderna. Denna metod används i tillämpningar av satellitradio. Denna moduleringsteknik kan implementeras genom reversibla logiska grindar. Utformningen av QPSK-tekniken kan göras med hjälp av VHDL-koden.

28). DDR SDRAM Controller Design & Implementering med hög hastighet

Det föreslagna systemet används för att utforma en DDR SDRAM-styrenhet för överföring av burstdata beroende på hög hastighet för att synkronisera dessa data mellan kretsarna i det inbäddade systemet och DDR SDRAM. Genom att använda VHDL-språket kan koden utvecklas.

29). 32 Â-bitars RISC Processor Design & Implementation

Huvudkonceptet för detta projekt är att implementera en 32-bitars RISC (reducerad instruktionsdator) med hjälp av ett verktyg som XILINK VIRTEX4. I detta projekt är 16 instruktionsuppsättningar utformade varhelst varje instruktion kan utföras i en enda CLK-cykel med hjälp av femfas pipelining-metoden.

30). Bussbro Implementering mellan AHB och OCP

Det föreslagna systemet används för att utforma en bussbro mellan två protokoll, nämligen gemensam och standard. Kommunikationsprotokollen som AHB (Advanced High-performance Bus) och OCP (Open Core Protocol) är mycket populära som används i applikationer av SoC (System On-chip) .

VLSI-projektidéer för ingenjörsstudenter

Listan över VLSI-projekt baserade på FPGA, MatLab, IEEE och Mini-projekt för ingenjörsstudenter listas nedan.

VLSI-projekt för M. Tech-studenter

Listan över VLSI-projekt baserade på M. Tech Students innehåller följande.

- Områdeseffektiv och mycket tillförlitlig RHBD-baserad I0T-minnescellsdesign som används i rymdapplikationer

- Fasdetektor med halvnivå för flera nivåer som används för CLK & Data Recovery Circuits

- Jämförare med låg effekt och hög hastighet som används för exakta applikationer

- Gated Voltage Level Translator med en högpresterande och integrerad multiplexer

- CNTFET-baserad Ternary Adder med högpresterande

- Magnitude Comparator Design med låg effekt

- Design of Threshold Logic Gate med nuvarande läge för fördröjningsanalys

- Mixed-Logic Line Decoders Design med låg effekt och hög prestanda

- Sleep Convention Logic Testability Design

- Spänningsnivåreglage för applikationer med dubbla försörjningar med en höghastighet och krafteffektiv

- Lågeffekt och lågspänning Double-Tail Comparator Design & Analys

- Flip-Flop-design baserad på pulsutlösare med låg effekt med hjälp av en signalgenomsläppningsmetod

- Effektiv kretsdesign baserad på Runtime omkonfigurerbara FET

- Magnitude Comparator Design med låg effekt

- Fördröj analys av logiska portdesigner med tröskelvärde för nuvarande läge

De FPGA-baserade VLSI-projekt för ingenjörsstudenter och CMOS VLSI design miniprojekt listas nedan.

- SEU Hardened Circuits Design & Characterization för FPGA baserat på SRAM

- En kompakt Memristor-baserad CMOS-hybrid LUT-design och potentiell applikation som används i FPGA

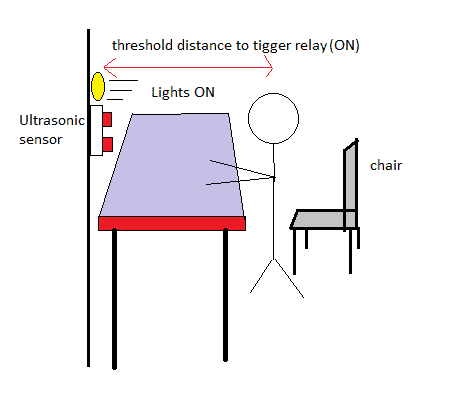

- Ultraljudsbaserad implementering av FPGA för avståndsmätning

- Implementering av FPGA för Booth Multiplier med Spartan6 FPGA

- Diskret Wavelet Transform baserat på lyft med Spartan3 FPGA

- ARM Controller i robotik med FPGA

- FPGA-baserad UART med flerkanalig

- Dämpning av EKG-signalbuller med FPGA

- UTMI-baserat FPGA Implementation & USB 2.0 Protocol Layer

- Implementering av medianfilter med Spartan3 FPGA

- AES algoritmbaserad implementering av FPGA

- Säkerhetsvarningssystem baserat på PIC för implementering av FPGA med Spartan 3an

- FPGA Implementation to Design the Controller for Remote Sensing Systems

- Bildbehandlingssats av FPGA med bildfiltrering av linjär och morfologisk

- Spartan3 FPGA-baserad medicinsk fusionsimplementering

Listan över VLSI mini-projekt med VHDL-kod innehåller följande.

- Jämförare med hög hastighet med VLSI

- En multiplikator för flytpunkt med VLSI

- VLSI-baserad konvertering av binär till grå

- Digitalt filter

- CLK Gating baserat på VLSI

- Vedisk multiplikator

- CMOS FF med VLSI

- Arkitekturen för parallellprocessor med VLSI

- VLSI-baserad Full Adder

- Design av DRAM / Dynamic Random Access Memory baserat på VLSI

- SRAM Layout baserat på VLSI

- VLSI-baserad digital signalprocessor

- VLSI-baserad multiplexer

- Design av MAC-enhet baserat på VLSI

- VLSI-baserad differentiator

- VLSI-baserad FFT eller Fast Fourier Transform

- Arkitekturen för Discrete Cosine Transform baserat på VLSI

- 16-bitars multiplikatordesign med VLSI19

- VLSI-baserad design av FIFO-buffert

- Höghastighetsaccelerator baserad på VLSI

VLSI-projekt med MATLAB & Xilinx

Listan över VLSI-projekt baserade på MATLAB- och VLSI-projekt som använder Xilinx innehåller följande.

- CDMA-modemdesign och analys med MATLAB

- FIR-filterdesign med VHDL på FPGA & MATLAB-baserad analys

- ModelSim & Matlab eller Simulink baserad simulering av system för bilteknik

- Xilinx-baserade tillägg som Ripple Carry & Carry Skip

- Aritmetisk enhet baserad på 32-bitars flytpunkt

- Floating Point-baserad ALU

- RISC-processor baserad på 32-bitars

- Konvolutionsmöjligheter i ortogonal kod

- Xilinx och Verilog-baserade varuautomater

- Xilinx-baserade Parallel Prefix Adders med 256-bitars

- Protokoll för ömsesidig autentisering med Xilinx

- Åtkomststruktur med encykel för logiskt test med Xilinx

- UTMI & Protocol Layer-baserad USB2.0 med Xilinx

- Konfiguration av datakomprimering och dekompression med Xilinx FPGA

- Xilinx 4000 baserade BIST & Spartan Series baserade FPGA

- IIR-filter baserat på MATLAB & VLSI

- FIR-filter med MATLAB

IEEE-projekt

De lista över IEEE VLSI-projekt listas nedan.

- VLSI-baserat trådlöst hemautomationssystem med Bluetooth

- Ta bort impulsljud i bilden med hjälp av en effektiv VLSI-arkitektur

- Arkitekturen för ett processor-i-minne för multimediekomprimering

- Övervakning av temperatursystem med Cloud & IoT

- OFDM-systemimplementering med IFFT & FFT

- Hamming Code Design & Implementation with Verilog

- VHDL-baserat fingeravtrycksigenkänning med Gabor-filter

- Aritmetiska funktioner Remapping med ROM Beroende på approximationsmetoder

- Analys av högeffektivitet och lågdensitetsprestanda för paritetskontrollkodavkodare i applikationer med låg effekt

- FFT Architectures with Feedforward of Pipelined Radix-2k

- Flip-flops-design för VLSI-applikationer med CMOS-teknik med hög prestanda

- FIR-filterdesign med uppslagstabell av Distribuerad aritmetik

- VLSI-baserad lågkostnads- och förbättrad bildskalningsprocessor

- ASIC Implementation & Design of a Advance Turbo Encoder & Decoder with 3GPP LTE

- Push-Pull-pulsade spärrar med låg effekt och höghastighetsvillkor

- Förbättrad skanning vid lågtestande skanningstest

- Aritmetic Coder VLSI Architecture for SPIHT

- Implementering av VHDL för UART

- VLSI-baserad spänningsregulator med lågt utfall

- Flash ADC Design med Enhanced Comparator Scheme

- Lågeffektmultiplikatordesign med sammansatt konstant fördröjningslogik

- Double Tail Comparator med hög prestanda och låg effekt

- Flashlagringssystem med hög prestanda beroende på skrivbuffert och virtuellt minne

- FF med låg effekt baserat på Sleepy Stack Approach

- LFSR Power Optimization för lågeffektiv BIST implementerad i HDL

- Varuautomatdesign och implementering med Verilog HDL

- Ackumulatordesign baserad på generationen av 3-viktmönster med LP-LSFR

- Reed-Solomon-avkodare med hög hastighet och låg komplexitet

- Snabbare Dadda multiplikator designteknik

- Digital demodulationsbaserad mottagare av FM-radio

- Generering av testmönster med BIST-scheman

- Implementering av VLSI-arkitektur med höghastighetsrörledning

- On-Chip Bus OCP-protokolldesign med bussfunktioner

- Fasfrekvensdetektor och laddningspumpdesign som används för högfrekvent faslåst slinga

- Cache Memory & Cache Controller Design med VHDL

- ASTRAN-baserad implementering av lågeffekt 3-2 & 4-2 adderkompressorer

- Förbetalt elfaktureringssystem med en On-Chip-design

- Överlappning av implementering med hjälp av logisk cell och dess kraftanalys

- Bär titt framåt Adder med olika bitprestationsanalys med VHDL

- Data Link Layer Design med Wi-Fi MAC Protokoll

- Implementering av FPGA för ömsesidigt autentiseringsprotokoll med modulär aritmetik

- PWM-signalgenerering med FPGA och variabel arbetscykel

Realtidsprojekt

Listan över VLSI-projekt i realtid omfattar främst VLSI-miniprojekt som använder VHDL-kod och VLSI-mjukvaruprojekt för ECE-ingenjörsstudenter.

- Pragmatisk integration av SRAM-radcache i heterogen 3-D DRAM-arkitektur med hjälp av TSV

- Inbyggd självtestteknik för diagnos av fördröjningsfel i klusterbaserade fältprogrammerbara grindmatriser

- ASIC Design of Complex Multiplier

- En billig VLSI-implementering för effektivt avlägsnande av impulsljud

- FPGA-baserad Rymdvektor PWM Kontroll IC för trefasinduktionsmotor

- VLSI Implementation of Auto Correlator and CORDIC Algorithm for OFDM Based WLAN

- Automatisk vägutsugning med högupplösta satellitbilder

- VHDL-design för bildsegmentering med hjälp av Gabor-filter för detektering av sjukdomar

- En turkodekoderarkitektur med låg komplexitet för energieffektiva trådlösa sensornätverk

- Förbättring av de ortogonala kodkonvolutionsmöjligheterna med hjälp av FPGA-implementering

- Design och Implementering av Floating Point ALU

- CORDIC design för fast rotationsvinkel

- Produkt Reed-Solomon-koder för implementering av NAND Flash Controller på FPGA-chip

- Statistisk SRAM-läsåtkomstförbättring med negativa kapacitanskretsar

- Energihantering av MIMO-nätverksgränssnitt på mobila system

- Design av datakrypteringsstandard för datakryptering

- Låg effekt och områdeseffektiv bärväljare

- Syntes och implementering av UART med VHDL-koder

- Förbättrade arkitekturer för en sammansmält enhet för flytande punkt-till-subtraktion

- En FPGA-baserad 1-bitars helt digital sändare som använder Delta-Sigma-modulering med RF-utgång för SDR

- Optimering av kedjesökningsanvändning i BCH-avkodaren för överföring av höga felfrekvenser

- Digital design av DS-CDMA-sändare med Verilog HDL och FPGA

- Design och implementering av effektiv systolisk matrisarkitektur

- En VLSI-baserad inlärningsalgoritm för robotdynamik

- En mångsidig multimediefunktionell enhetsdesign med den rasande kraftdämpningstekniken

- Design av bussbro mellan AHB och OCP

- Behavioral Synthesis of Asynchronous Circuits

- Hastighetsoptimering av en FPGA-baserad modifierad Viterbi-avkodare

- Implementering av I2C-gränssnitt

- En höghastighets- / lågeffektsmultiplikator med hjälp av en avancerad rasande kraftdämpningsteknik

- Fastspänning av den virtuella matningsspänningen för strömförsörjda kretsar för aktiv läckreduktion och tillförlitlighet för grindoxid

- FPGA-baserad effekteffektiv kanaliserare för programvarudefinierad radio

- VLSI Architecture och FPGA Prototyping av en digitalkamera för bildsäkerhet och autentisering

- Driftförbättring av inomhusrobot

- Design och implementering av ett ON-Chip Permutation Network för Multiprocessor System-On-Chip

- En synkroniseringsmetod för symbolhastighet för trådlösa OFDM-system med låg effekt

- DMA-kontroller (direktminnesåtkomst) med VHDL / VLSI

- Omkonfigurerbar FFT med CORDIC-baserad arkitektur för MIMI-OFDM-mottagare

- Spurious Power Suppression Technique för multimedia / DSP-applikationer

- Effektiviteten hos BCH-koder vid digital bildvattenmärkning

- Dual Data Rate SD-RAM-styrenhet

- Implementering av Gabor-filter för fingeravtrycksigenkänning med Verilog HDL

- Utformning av en praktisk nanometerskala överflödig via medveten standardcellbibliotek för förbättrad redundant via 1 insättningshastighet

- En förlustfri datakomprimeringsalgoritm och dess hårdvaruarkitektur

- Ett ramverk för korrigering av mjuka fel med flera bitar

- Viterbi-baserad effektiv testdatakomprimering

- Implementering av FFT / IFFT-block för OFDM

- Wavelet-baserad bildkomprimering med VLSI Progressive Coding

- VLSI-implementering av fullständigt pipelinerad multiplikator mindre 2d DCT / IDCT-arkitektur för Jpeg

- FPGA-baserad felemulering av synkrona sekventiella kretsar

Således handlar det här om listan över VLSI-projekt för teknik, M.Tech-studenter som är användbara för att välja deras sista årets projektämne. Efter att ha tillbringat din värdefulla tid medan du har gått igenom den här listan tror vi att du har en ganska bra uppfattning om att välja det projektämne du väljer från VLSI-projektlistan och hoppas att du har tillräckligt med självförtroende för att ta upp något ämne från lista. För ytterligare information och hjälp med dessa projekt kan du skriva till oss i kommentarfältet nedan. Här är en fråga till dig, vad är VHDL?

Fotokredit

- VLSI-projekt av set-tech