Multiplikatorer används i ett brett spektrum av digital signalbehandling och andra applikationer. På grund av framsteg inom nuvarande teknik har många forskare huvudsakligen koncentrerat sig på designfaktorerna för bättre prestanda. Några av designmålen är - hög hastighet, noggrannhet, låg strömförbrukning, layoutens regelbundenhet, mindre area. DSP-processor har olika beräkningsblock, som multiplexrar, tillsatser, MAC . Drift- och körhastigheten för dessa block har avancerat jämfört med tidigare versioner. Körningshastigheten för multiplikatorer beror på två faktorer, halvledarteknik och multiplikatorarkitektur. Adders är den grundläggande byggstenen för digitala multiplexers, där vi utför en serie upprepade tillägg, för att påskynda multiplikatoroperationen måste adderarens operationshastighet ökas. Det finns många applikationer för digital signalbehandling där kritisk fördröjningsväg och processorns prestanda ligger i multiplikatorn. Det finns olika typer av multiplikatorer, bland vilka 4 × 4 array-multiplikatorn är en avancerad som beskrivs i den här artikeln.

Multiplikationsscheman i 4 × 4 Array Multiplier

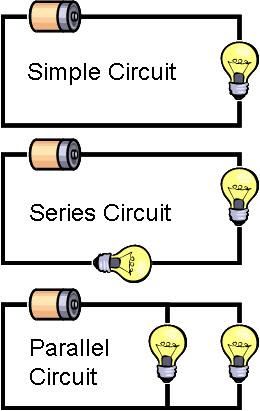

Det finns två typer av multiplikationsscheman de är

Seriemultiplikation (Skift – Lägg till): Den seriella multiplikationsåtgärden kan lösas genom att hitta partiella produkter och sedan lägga till partiella produkter tillsammans. Implementationerna är primitiva med enkel arkitektur

Parallell multiplikation: De parallella produkterna genereras samtidigt i parallell multiplikation och en högpresterande maskin Parallella implementeringar tillämpas, latens minimeras.

Multiplikationsalgoritm

Multiplikationsprocessen har tre huvudsteg:

- Partiell produktgenerering

- Delvis produktreduktion

- Sista tillägget.

Den vanliga multiplikationsmetoden är 'lägg till och skift' -algoritmen. Multiplikationsalgoritmen för en N-bitmultiplikator visas nedan.

4-för-4-multiplikation

4 - av - 4 - multiplikation 1

exempel-2

Partiella produkter genereras med AND-grindar, där

- Multiplikand = N-bitar

- Multiplikator = M-bitar

- partiella produkter = N * M.

Multiplikationen av två 8-bitars nummer, som genererar 16-bitarsprodukten.

Tilläggsekvationen är

P (m + n) = A (m). B (n) = i = 0 m-1∑ j = 0n-1∑ ai bj 2i + j ……. 1

A, B = 8 bitar

Steg i multiplikation

Följande är stegen för multiplikation

- Om LSB för multiplikator är '1'. lägg sedan till multiplicand i en ackumulator multiplikatorbit flyttas en bit till höger och multiplicand bit flyttas en bit till vänster.

- Stoppa när alla bitar i multiplikatorn är noll.

- Mindre hårdvara används om partiella produkter läggs till seriellt. Vi kan lägga till alla PP med en parallell multiplikator. Det är emellertid möjligt att använda kompressionsteknik, antalet partiella produkter kan reduceras innan tillsats utförs.

Olika typer av multiplikatorer

De olika typerna av multiplikatorer är,

Båsmultiplikator

Funktionen för monterens multiplikator är att multiplicera två signerade binära nummer som representeras i 2-komplement form. Fördelarna med båsmultiplikatorer är minimikomplex, multiplikation påskyndas. Nackdelarna med båsmultiplikatorer är Strömförbrukningen är hög.

Kombinationsmultiplikator

Kombinationsmultiplikatorn utför multiplikation av två osignerade binära tal. Fördelen med en kombinationsmultiplikator är att den lätt kan generera mellanprodukter. Den största nackdelen med kombinationsmultiplikatorn är att den upptar stora områden.

Sekventiell multiplikator

Multiplikation är uppdelad i sekvensen av steg, där den genererade partiella produkten läggs till i ackumulatorns partiella summa nu flyttas till nästa steg. Fördelen med detta är att det upptar mindre yta. Nackdelen med en sekventiell multiplikator är att det är en långsam process.

Wallace-trädmultiplikator

Det minskar antalet partiella produkter och använder bärval-adderare för tillsats av partiella produkter. Fördelen med Wallace-trädmultiplikatorn är en höghastighets- och medelkomplex design. Den största nackdelen med Wallace-trädmultiplikatorn är att layouten är oregelbunden och upptar ett större område.

Array Multiplier

Multiplikatorkretsen är baserad på add shift-algoritmen. Den största fördelen med arraymultiplikatorn är att den är enkel i design och regelbunden i form. Nackdelen med en arraymultiplikator är att förseningen är hög och hög strömförbrukning.

Skift och lägg till multiplikator

Det liknar den normala multiplikationsprocessen, som vi gör i matematik, från matrismultiplikatorflödeschatt där X = Multiplikand Y = Multiplikator A = Ackumulator, Q = Kvot. Först kontrolleras Q om det är 1 eller nej om det är 1, lägg sedan till A och B och förskjut A_Q aritmetik till höger, annars om det inte är 1 direkt förskjut A_Q aritmetisk höger och minska N med 1, i nästa steg kontrollera om N är 0 eller nej. Om N inte 0 upprepas från Q = 0 steg annars avsluta processen.

skift-och-lägg till-multiplikator

Konstruktion och bearbetning av en 4 × 4-multiplikator

Arbetsmultiplikatorns designstruktur är regelbunden, den är baserad på add shift algoritmprincipen.

Delprodukt = multiplikator * multiplikatorbit ...……. (2)

där OCH-grindar används för produkten görs summeringen med Fulladders och Half Adders där delprodukten flyttas enligt deras bitorder. I en multiplikator för n * n-array beräknar n * n OCH-grindar delprodukterna och tillsatsen av partiella produkter kan utföras med hjälp av n * (n - 2) Fulladdare och n Half adders. Den multiplikator som visas på 4 × 4 har 8 ingångar och 8 utgångar

4-för-4-array-multiplikator

Byggstenar med 4 × 4 Array Multiplier

En hel adderare har tre ingångsrader och två utgångslinjer, där vi använder detta som en grundläggande byggsten för en arraymultiplikator. Följande är exemplet på en 4 × 4 array-multiplikator. Den vänstra biten är LSB-biten av partiell produkt.

adder-block-diagram

array-multiplier-block-diagram

Den rätta biten är MSB-biten av partiell produkt. Delprodukterna flyttas nu mot vänster vid multiplikation och de läggs till för att få slutprodukten. Denna process upprepas tills inga två partiella produkter går ut för tillsats.

4-av-4-multiplikation-1

logik-diagram-av-4-för-4 - array - multiplikator

Där a0, a1, a2, a3 och b0, b1, b2, b3 är multiplikand och multiplikator, är summering av alla produkter delprodukter. Resultatet av summan av delprodukten är en produkt.

För en 4 × 4-arraymultiplikator behöver den 16 OCH-grindar, 4 halvaddrar (HA), 8 fullständiga tillsatser (FA). Totalt 12 tillägg.

Fördelar med 4 × 4 Array Multiplier

Fördelarna med array-multiplikator är,

- Minsta komplexitet

- Lätt skalbar

- Lätt rörledd

- Regelbunden form, lätt att placera och föra

Nackdelar med 4 × 4 Array Multiplier

Nackdelarna med arraymultiplikator är följande:

- Hög strömförbrukning

- Mer digitala grindar vilket resulterar i stora områden.

Tillämpningar av 4 × 4 Array Multiplier

Applikationerna för arraymultiplikator listas,

- Arraymultiplikator används för att utföra aritmetisk operation , som filtrering, Fourier-transform, bildkodning.

- Snabb drift.

Således handlar det här om 4 × 4 array multiplikator som är en avancerad multiplikator baserad på add and shift-princip, kan prestandan enkelt ökas med pipeline-tekniken med enkel konstruktion, även om den använder fler logiska grindar där den kan implementeras med Verilog. Här är en fråga, 'Hur många logiska grindar krävs för att designa 3 * 3 arraymultiplikator?'.