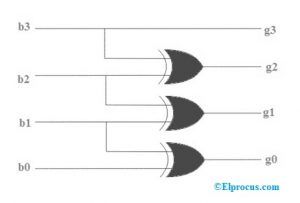

Med hjälp av en uppsättning spärr / återställningsnätverk blir det möjligt att låta en logik röra sig i en framåtriktad sekvens, slå på en given uppsättning utgångar HÖG, som svar på en växlande ingångsklocka. Och när maxgränsen har uppnåtts börjar ingångsklockorna att stängas av eller dra tillbaka sekvensen i motsatt ordning.

Sålunda styrs upp-ned-sekvensen genom en enda oscillerande ingångsklocksignal.

Processen kan också förklaras enligt följande:

Som svar på en tillämpad omkopplingsklocka börjar kretsen lägga till HÖG logik vid utgångarna i en inkrementerande sekvens och när den maximala gränsen har uppnåtts börjar den subtrahera HIGH från utgången genom att göra dem LÅG i motsatt sekvens, som svar på den klocksignaler.

Här visas endast 4 utgångar sedan IC 4043 har endast 4 par inställnings- / återställningsspärrar ändå kan antalet möjligen ökas genom att kaskadera IC 4017 och genom att lägga till ytterligare 4043 IC med den befintliga. Detta skulle göra det möjligt för oss att få 8 siffror för sekvensering / återställning eller 8 par upp / ner-utgångar.

Ansökan

Denna krets kan vara mycket användbar för att styra en given parameter så att varje ytterligare ökning av parametern inhiberas så snart den maximala gränsen överskrids, och omvänt återställs och initieras processen när gränsen kommer tillbaka inom intervallet.

Till exempel kan den appliceras i små hissar för att endast tillåta 3 personer att komma in i hissen, när denna gräns överskrids hindras hissen från att starta, men när gränsen har återställts får hissen röra sig.

Hur denna UPP / NED-sequencer fungerar

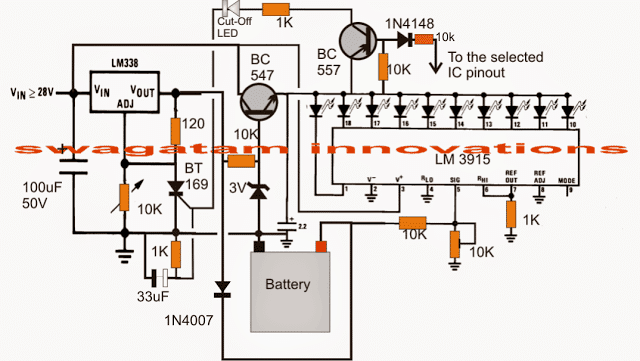

Denna krets skapades ursprungligen för att starta strömförsörjningar i sekvens och sedan stänga av dem för en andra gång i motsatt ordning. Denna funktion kan ofta vara användbar för att tippa med utrustning och kretsar där ström måste användas och tas ut i en specifik ordning.

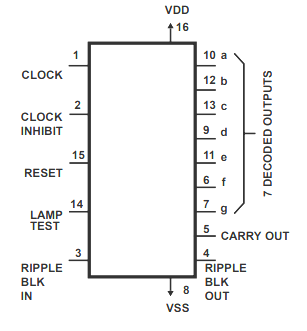

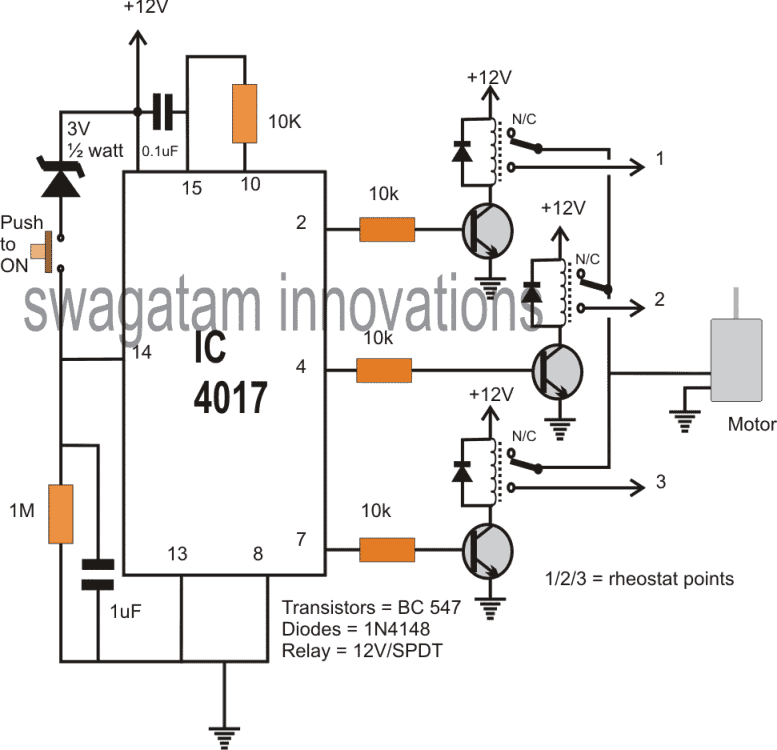

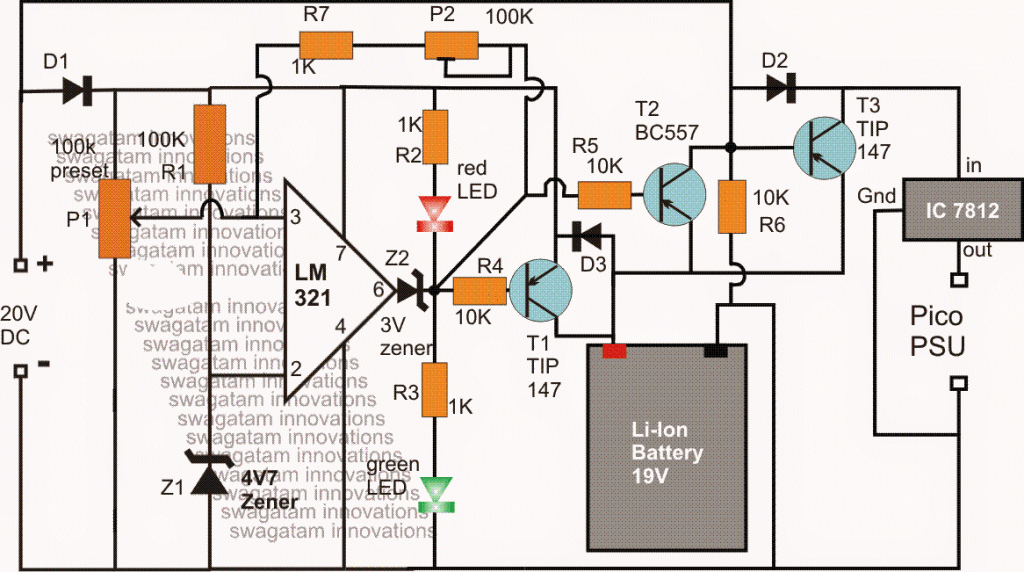

Huvuddelen av kretsen är arbetshäst IC 4017 CMOS decennieräknare. Utgångarna Q1 till Q4 är vana vid att skapa spärrar i serie i storleksordningen 1-2-3-4, varefter räkningen stoppas. Genom att trycka på omkopplaren S1 kan räkningen fortsätta, och nu tillämpas räknarutgångarna Q5 till Q8 för att återställa spärrarna i motsatt ordning, vilket betyder i ordningen 4-3-2-1. Den sista utgången, Q9, används för att stoppa räknaren.

Så snart strömmen slås PÅ gör C2 och R2 först räknaren i återställningsläge. När strömförsörjningsspänningen har blivit stabil går återställningssignalen så småningom så att 4017 kan börja räkna vid 1-Hz klocksignalen som erhålls genom en oscillator bestående av IC1d, R3 och C3.

De utgångsstift av IC 4017 utlöses i följd med varje stigande kant på klockpulsen. Men när följande klockpuls anländer stängs den sista utgången.

Spärrarna i fyrkants RS-spärrtyp 4043 gör det möjligt för utgångarna att förbli aktiverade. IC2 upphör att räkna vid Q4 på grund av IC1b som tar bort klockaktiveringssignalen vid stift 13 till och med IC1a.

För att tillåta 4017 att fortsätta räkna och därför stänga av utgångarna, måste S1 tryckas, vilket återställer klockaktiveringen vid stift 13.

Räkneutgångar Q5 till Q8 är kopplade till spärrenas återställningsingångar, så när IC2-sekvensen rör sig nedåt, återställs spärrarna i omvänd riktning. Räkneprocessen upphör så småningom vid Q9 av IC lc, som ännu en gång tar bort klockaktiveringssignalen.

Högt mottagande motstånd med låg ström (R4-R7) används på ingångarna för spärråterställning för att undvika odefinierade startsituationer.

Dellista

Motstånd (Alla motstånd är 1/4 watt 5%)

R1 = 4K7

R3 = 4M7

R2, R4, R5, R6, R7 = 1M

Kondensatorer

Cl, C4, C5 = 0,1 uF / keramik

C2 = 22uF / 25V

C3 = 1uF / 25V

Integrerade kretsar

IC 4017 = 1 nr

IC 4043 = 1 nr

IC 4093 = 1 nr

S1 = tryck på ON-omkopplaren

Tidigare: Motorcykelknapp Startlåsningskrets Nästa: DC Biasing in Transistors - BJTs